# **EPISTAR**

## **ES-VEBCA12C**

InGaN A-series Blue LED Chip

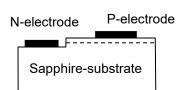

## > Mechanical Specification:

#### (1) Dimension

- Chip size: 305  $\pm$  25  $\mu m$  x 305  $\pm$  25  $\mu m$

- Thickness: 110  $\pm$  10  $\mu m$  - P bonding pad: 90  $\pm$  10  $\mu m$  - N bonding pad: 90  $\pm$  10  $\mu m$

#### (2) Metallization

Topside P electrode: Au alloyTopside N electrode: Au alloy

#### **Features:**

- · High radiant flux

- · Long operation life

- · Lambertian radiation

### **Applications:**

Automotive

# > Electro-optical Characteristics at 25°C: (1)

| Parameter                          | Symbol |     | Condition | Min. | Тур. | Max. | Unit |

|------------------------------------|--------|-----|-----------|------|------|------|------|

| Farmer d Vallage                   | Vf1    |     | If = 10μA | 2.0  | -    | -    | V    |

| Forward Voltage                    | Vf2    |     | If = 20mA | -    | 2.9  | 3.2  | V    |

| Reverse Current                    | Ir     |     | Vr = 5V   | -    | -    | 1.0  | μΑ   |

| Dominant Wavelength <sup>(2)</sup> | λd     |     | If = 20mA | 450  | -    | 470  | nm   |

| Spectra Half-width                 | Δλ     |     | If = 20mA | -    | 25   | -    | nm   |

| Radiant Flux <sup>(3)(4)</sup>     | Ро     | A29 | If = 20mA | 28   | -    | 29   | mW   |

|                                    |        | A30 |           | 29   | -    | 30   |      |

|                                    |        | A31 |           | 30   | -    | 32   |      |

|                                    |        | A32 |           | 32   | -    | 34   |      |

|                                    |        | A33 |           | 34   | -    | 36   |      |

#### Note:

(1) ESD protection during chip handling is recommended.

(2) Basically, the wavelength span is 20nm; however, customers' special requirements are also welcome.

(3) Radiant flux is determined by using an Ag-plated TO-can header without an encapsulant

(4) Radiant flux measurement allows a tolerance of  $\pm 15\%$ .

# > Absolute Maximum Ratings:

| Parameter                                 | Symbol | Condition                   | Rating      | Unit |

|-------------------------------------------|--------|-----------------------------|-------------|------|

| Forward DC Current                        | If     | Ta = 25℃                    | ≤ 50        | mA   |

| Reverse Voltage                           | Vr     | Ta = 25℃                    | ≤ 5         | V    |

| Junction Temperature                      | Tj     | -                           | ≤ 125       | ۲    |

| ESD withstand voltage(HBM) <sup>(2)</sup> | VESD   | -                           | Up to 2     | KV   |

| Storage Temperature                       | Tstg   | Chip                        | -40 ~ +85   | Ĉ    |

|                                           |        | Chip-on-tape/storage        | 5 ~ 35      | Ĉ    |

|                                           |        | Chip-on-tape/transportation | -20 ~ +65   | Ĉ    |

| Temperature during Packaging              | -      | -                           | 280(<10sec) | ٢    |

Note: (1) Maximum ratings are package dependent. The above maximum ratings were determined using a Printed Circuit Board (PCB) without an encapsulant. Stresses in excess of the absolute maximum ratings such as forward current and junction temperature may cause damage to the LED.

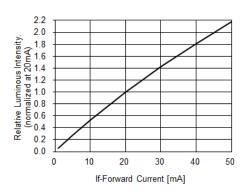

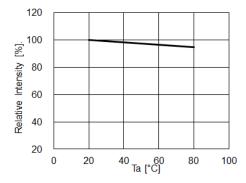

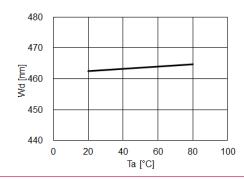

### > Characteristic Curves:

Fig.1 – Relative luminous Intensity vs. Forward Current

Fig.3 – Relative Intensity (@20mA) vs. Ambient Temperature

Fig.5 – Dominant Wavelength (@20mA) vs. Ambient Temperature

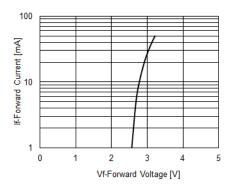

Fig.2 – Forward Current vs. Forward Voltage

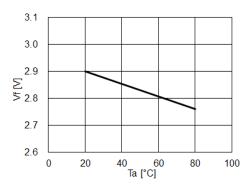

Fig.4 – Forward Voltage (@20mA) vs. Ambient Temperature

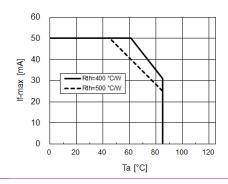

**Fig.6** – Maximum Driving Forward DC Current vs. Ambient Temperature (De-rating based on Tj max. = 125°C)

<sup>(2)</sup> According to ANSI/ESDA/JEDEC JS-001

## > Qualification:

- <sup>1)</sup> EPISTAR's LED chips and epi-wafers are designed and manufactured according to the quality management system that complies to the IATF 16949:2016 requirements (IATF No: 0325277/ Certificate Registration No: 20000910 IATF16).

- <sup>2)</sup> The chip qualification test plan is based on the guidelines of AEC-Q101-REV-D, Failure Mechanism Based Stress Test Qualification for Discrete Semiconductors in Automotive Applications.

## > Revision:

| Version | Yersion Page |                 | Date of Modification |  |

|---------|--------------|-----------------|----------------------|--|

| А       | 3            | Initial Release | December, 2019       |  |